# Implementation of neurobiological and various signal processing algorithms using FPGA circuits

## PhD Thesis

László Schäffer

Supervisors: Szilveszter Pletl, PhD and Zoltán Kincses, PhD

Doctoral School of Computer Science

Department of Technical Informatics

Faculty of Science and Informatics

University of Szeged

Szeged 2021

# **Contents**

| 1 | Intr | oductio | on                                                             | 1  |

|---|------|---------|----------------------------------------------------------------|----|

|   | 1.1  | Contri  | butions                                                        | 3  |

| 2 | FPG  | A-base  | d real-time detection and synthesis of neurophysiological sig- |    |

|   | nals |         |                                                                | 5  |

|   | 2.1  | Introd  | uction                                                         | 5  |

|   | 2.2  |         | d Works                                                        | 7  |

|   | 2.3  | Overa   | ll system architecture                                         | 9  |

|   |      | 2.3.1   | Electrophysiological Recording                                 | 10 |

|   |      | 2.3.2   | Pre-processing IIR Filter                                      | 10 |

|   |      | 2.3.3   | Processing - FPGA                                              | 10 |

|   |      | 2.3.4   | Host PC                                                        | 10 |

|   | 2.4  | Neura   | l Signal Generator                                             | 11 |

|   |      | 2.4.1   | Spike Generation Requirements                                  | 11 |

|   |      | 2.4.2   | Mersenne Twister Random Number Generator                       | 12 |

|   |      | 2.4.3   | FPGA architecture                                              | 13 |

|   |      | 2.4.4   | Implementation Results                                         | 15 |

|   |      | 2.4.5   | Conclusion                                                     | 17 |

|   | 2.5  | Compa   | arison of spike detection algorithms                           | 17 |

|   |      | 2.5.1   | Non-Linear Energy Operator                                     | 18 |

|   |      | 2.5.2   | Power Method                                                   | 18 |

|   |      | 2.5.3   | Amplitude Thresholding (Positive, Negative, Absolute)          | 19 |

|   |      | 2.5.4   | Cross-Correlation Based Spike Detection                        | 20 |

|   |      | 2.5.5   | Evaluation                                                     | 21 |

|   |      | 2.5.6   | Results and Conclusion                                         | 22 |

|   | 2.6  | Multi-  | channel Spike Detection                                        | 22 |

|   |      | 2.6.1   | Spike Detection Algorithm                                      | 23 |

|   |      | 2.6.2   | FPGA Architecture of Spike Detection                           | 25 |

|   |      | 2.6.3   | Results and Discussion                                         | 27 |

|   | 2.7  | Discus  | ssion and concluding remarks                                   | 28 |

|   | 2.8  | Contri  | butions                                                        | 28 |

| 3 | FPG  | A-base | d real-time classification of neurophysiological signals taking  |    |

|---|------|--------|------------------------------------------------------------------|----|

|   | into | accou  | nt spatial information                                           | 29 |

|   | 3.1  | Introd | uction                                                           | 29 |

|   | 3.2  | Relate | d Works                                                          | 31 |

|   | 3.3  | Spatia | l information based OSort for real-time spike sorting using FPGA | 31 |

|   |      | 3.3.1  | FPGA architecture                                                | 34 |

|   |      | 3.3.2  | Implementation Results                                           | 36 |

|   |      | 3.3.3  | Validation Results                                               | 37 |

|   |      | 3.3.4  | Discussion                                                       | 40 |

|   |      | 3.3.5  | Comparison to other systems                                      | 41 |

|   |      | 3.3.6  | Scalability and Limitations                                      | 42 |

|   | 3.4  | Discus | sion and concluding remarks                                      | 43 |

|   | 3.5  | Contri | butions                                                          | 44 |

| 4 | FPG  | A impl | ementations in the field of signal processing and simulation     | 45 |

|   | 4.1  | Introd | uction                                                           | 46 |

|   |      | 4.1.1  | Face recognition                                                 | 46 |

|   |      | 4.1.2  | Pose estimation and sensor fusion                                | 46 |

|   |      | 4.1.3  | Suspension control                                               | 46 |

|   |      | 4.1.4  | Wind turbine modelling                                           | 47 |

|   | 4.2  | Relate | d Works                                                          | 48 |

|   |      | 4.2.1  | Face recognition                                                 | 48 |

|   |      | 4.2.2  | Pose estimation with sensor fusion                               | 48 |

|   |      | 4.2.3  | Active suspension control                                        | 49 |

|   |      | 4.2.4  | Wind Turbine modelling                                           | 50 |

|   | 4.3  | FPGA-  | based low-cost real-time face recognition                        | 51 |

|   |      | 4.3.1  | Eigenfaces method                                                | 51 |

|   |      | 4.3.2  | Eigenface Calculation                                            | 53 |

|   |      | 4.3.3  | Classification                                                   | 54 |

|   |      | 4.3.4  | Overall System                                                   | 54 |

|   |      | 4.3.5  | FPGA implementation                                              | 55 |

|   |      | 4.3.6  | Results                                                          |    |

|   |      | 4.3.7  | Conclusion                                                       | 58 |

|   | 4.4  | A real | -time pose estimation algorithm based on FPGA and sensor fusion  | 58 |

|   |      | 4.4.1  | Measurement Setup                                                | 58 |

|   |      | 4.4.2  | Sensor Fusion                                                    | 60 |

|   |      | 4.4.3  | FPGA system architecture                                         | 62 |

|   |      | 4.4.4  | Implementation                                                   |    |

|   |      | 4.4.5  | Results                                                          |    |

|   |      | 446    | Extension with ITMR-based module for indoor localization         | 65 |

|         | 4.4.7 Conclusion                                                   |  |

|---------|--------------------------------------------------------------------|--|

| 4.5     | Implementation of an FPGA-based actual observer for active suspen- |  |

|         | sion control                                                       |  |

|         | 4.5.1 Active suspension system model                               |  |

|         | 4.5.2 Actual observer                                              |  |

|         | 4.5.3 FPGA architecture                                            |  |

|         | 4.5.4 Results                                                      |  |

|         | 4.5.5 Conclusion                                                   |  |

| 4.6     | Implementation of an FPGA-based wind turbine HIL model 76          |  |

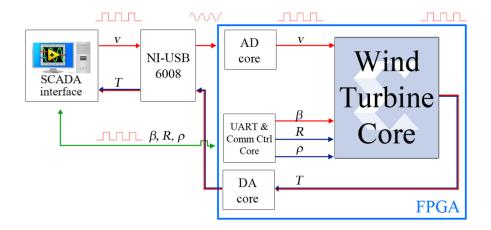

|         | 4.6.1 System setup                                                 |  |

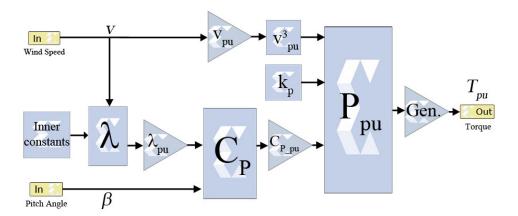

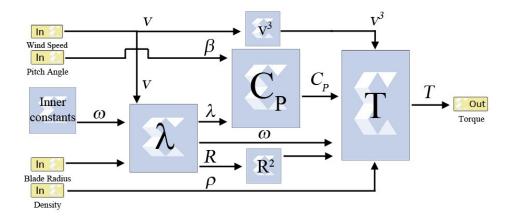

|         | 4.6.2 Wind Turbine model                                           |  |

|         | 4.6.3 FPGA implementation                                          |  |

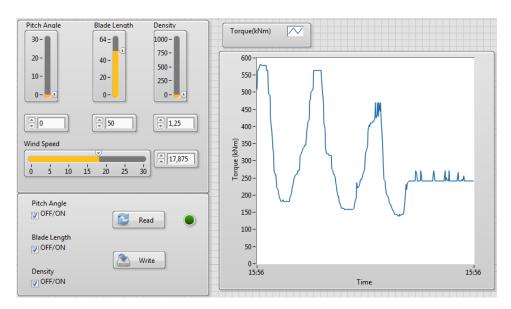

|         | 4.6.4 Results                                                      |  |

|         | 4.6.5 Conclusion                                                   |  |

| 4.7     | Discussion and concluding remarks                                  |  |

| 4.8     | Contributions                                                      |  |

| Bibliog | raphy 89                                                           |  |

| Summa   | 101                                                                |  |

| Összefo | oglalás 107                                                        |  |

| Publica | ntions 113                                                         |  |

# Chapter 1

# Introduction

Signal processing is an important part of computer science, which is used in but not limited to automation, pattern recognition, control theory, artificial intelligence, and networking and communication. A signal can be anything, which is measurable and everything that can be measured is also can and inevitably will be processed using analog or digital signal processing methods. It can be a temperature measurement, an image from a camera or a recording of neural brain activity, all of them have to be processed in some way. In signal processing the first step is to measure a physical quantity. After the measurement the quantity can be filtered and amplified. In ideal circumstances a noise-free and proper amplitude quantity can be converted to a digital signal using an analog-digital converter (ADC). This digital signal can be processed by a Central Processing Unit (CPU) / microprocessor, a microcontroller, a Graphics Processing Unit (GPU), a Field Programmable Gate Array (FPGA) or an Application-Specific Integrated Circuit (ASIC).

There are various hardware and also software solutions in signal processing. All hardware types have their role in different circumstances and environments, which depends on performance, reliability, power consumption and form-factor. Nowadays CPUs are widely used in personal computing, although they also widely used for data processing with high performance, but at a cost of high power consumption and better sequential processing than parallel. Microcontrollers as their name suggests are used for controlling automated devices, and can be found in almost every household appliances due to their small form-factor and low power consumption. GPUs are used for gaming in personal computing, but also widely used for data processing, mainly for neural networks and crypto mining, which are complex parallel computing demanding problems. Unfortunately GPUs are big, with high energy consumption and require an operating system with a CPU to function. On the other hand FPGAs and ASICs are small form-factor, low energy consumption devices with medium to high performance due to their parallel computing capabilities, and a CPU can be implemented on their surface too, but they are far behind in sequential computing

2 Introduction

performance.

In performance demanding applications the usage of GPUs, FPGAs or ASICs are inevitable, due to their parallel computation capabilities. When low power consumption is required usually FPGAs or ASICs are used, but the prototyping step is always done on FPGAs, because of their true parallel nature and yet flexibility for reprogramming. FPGAs can be applied for all problems, but their real usefulness comes in those where the algorithm can be separated into independent side-by-side running tasks. FPGAs are programmable semiconductor devices, which consists of a matrix of programmable logic elements connected through programmable interconnections. The basic structure of a Xilinx FPGA is built up from Configurable Logic Blocks (CLBs), a Programmable Interconnection (PI) network, Block RAM memories (BRAMs), configurable I/O Blocks (IOBs), Digital Signal Processors (DSP) and Digital Clock Management (DCM) blocks. The CLBs are the main digital processing blocks, which are capable of performing combinational as well as sequential operations. For complex arithmetic operations DSP blocks can be used, while internal data storage can be done with BRAMs. FPGA architectures can contain embedded soft or hard core microprocessors (MicroBlaze, ARM processor cores), support numerous data communication protocols (USB, Ethernet, SPI, I2C, UART, etc.) and additional peripherals. It is no surprise then that FPGAs are already used in off-the-shelf neural recording systems (e.g. Intan), but usually in the measurement part due to the high bandwidth requirements with densely packed electrode arrays. There is a scientific progress for using FPGAs not only in measurement, but for neural signal processing at the same time, which opened a way for online or real-time spike sorting methods.

This work presents FPGA-based acceleration of signal processing algorithms ranging from neurophysiological signal detection, classification, synthesis through hardware-in-the-loop simulation to control theory. The relation between the presented solutions is that instead a solely software-based optimization a new parallel FPGA architecture has been developed, which makes these algorithms operate more efficiently and in real-time. Furthermore FPGA-based solutions can be used in otherwise inaccessible environments.

Changing the hardware in signal processing applications are a complex task and usually requires to modify an optimised software. In many cases only software optimisation offers limited improvements, although the time and energy investment is still significant. In these cases the usage of FPGA makes possible to rapidly change the hardware architecture along with the software.

In Chapter 2., an FPGA-based multi-channel neurophysiological action potential signal detection approach is presented along with an also multi-channel template-based neural signal pattern generator. The main idea is to take advantage of the parallel nature of the FPGA architecture to handle multiple electrode channels at the same time. A problem arises with the detection algorithm selection, which needs

1.1 Contributions 3

to be simple, but efficient. Another problem is the validation of the proposed solution, which requires a multi-channel real-time neural measurement. To solve this a real-time neural signal generator architecture is proposed, which generates action potentials on multiple channels considering among other important factors the spatial information like the crosstalk and the amplitude decay between adjacent channels.

In Chapter 3., an FPGA-based architecture is presented for multi-channel neural signal classification. The problem is that a simple, but efficient spike classification algorithm is required. Most of the spike sorting algorithms works offline and have unfeasible requirements for real-time operation such as storing the entire measurement before the processing takes place. There are already online spike sorting solutions, which can be used, but only for single-channel processing. Therefore an already available template-based unsupervised online spike sorting algorithm is chosen to modify it to be capable of multi-channel processing. Furthermore using a closely packed electrode array allows to exploit the small distances between electrode channels and use the spatial information to make the classification more precise.

In Chapter 4., different signal processing algorithms are accelerated using FPGAs to make real-time usage available, moreover form-factor and power consumption are also taken into consideration. It is an all-around presentation of FPGA capabilities with rapid prototyping to prove that vastly different algorithms can be efficiently applied with FPGAs for real-time operation. Different fields of computer science are chosen such as control theory, hardware-in-the-loop simulation and pattern recognition.

These chapters present different signal processing FPGA applications, however similarities can be noticed. FPGA-based acceleration links them together, which leads to more efficient and real-time solutions. Also from sequential operation a more parallel approach can be seen for which a change in the current algorithm development perspective is required. Furthermore in each chapter is a comparison between the regular and the proposed solution, which emphasises the benefits of FPGA-based systems.

# 1.1 Contributions

The ideas, figures, tables and results included in this thesis were published in scientific papers (listed at the end of the thesis). In a nutshell, the author is responsible for the following contributions:

**Chapter 2.**: The algorithmic descriptions and architectures of multi-channel action potential detection and hybrid template-based neural signal generator.

Chapter 3.: The idea and architecture of multi-channel online sorting using spatial

4 Introduction

information.

**Chapter 4.**: Real-time operation of signal processing methods and simulation using FPGA. Real-time operating FPGA implementation of face recognition, sensor fusion, active suspension control and wind turbine HIL simulation are presented.

# Chapter 2

# FPGA-based real-time detection and synthesis of neurophysiological signals

Neurophysiological signal detection has been an area of active research in recent decades. Many algorithms and systems were developed to create reliable solutions. In this chapter a real-time multi-channel FPGA-based neurophysiological signal detector is introduced together with an a neurophysiological template-based signal generator for validation purposes.

The main novelties of the work are a multi-channel Non-Linear-Energy Operator (NEO) based multi-channel neural signal detector FPGA architecture capable of detecting on 128 different electrodes in real-time and a multi-channel neural signal generator, which can generate signals on 128 channels in real-time. The randomness of the neural signal generator is provided by a Mersenne-Twister based pseudo random number generator FPGA architecture working in real-time.

The structure of the chapter is as follows. Section 2.1 and Section 2.2 introduce the problem, summarizes the related works and briefly presents previous results. The description of the overall spike sorting system is presented in Section 2.3. The description of the neurophysiological signal generator is presented in Section 2.4. The comparison of various spike detection algorithms are covered in Section 2.5. The algorithmic description and architecture of the proposed multi-channel spike detection are covered in Section 2.6. Result and final thoughts are summarized in Section 2.8.

#### 2.1 Introduction

The brain is one of the most complex biological systems containing quadrillions of synapses and billions of neurons. To study this organ in humans or in animal models,

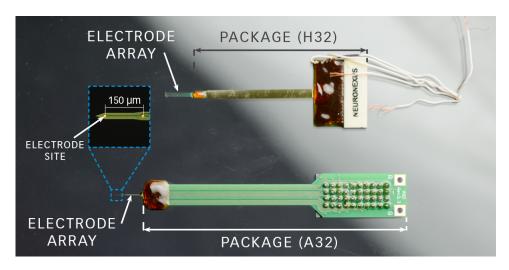

and to examine elementary neuronal mechanisms or high-order brain functions, such as learning, sleeping, perception and memory, a widely used method can be applied: the extracellular measurement of the electrical activity in the brain. During a typical *in vivo* electrophysiological experiment a single or multiple neural implants comprising dozens of small electrodes are inserted into the brain tissue for recording short, electrical impulses (usually referred to as action potentials or spikes) generated by neurons located close to the implanted devices. In Fig. 2.1 an example can be seen for neural probes.

**Figure 2.1:** Example of neural probes for measurements. [1]

The obtained signals contain the trains (sequences) of action potentials fired by neurons located around the electrodes of the neural probe [2, 3].

Using a high electrode density ( $<20~\mu m$  electrode-pitch) is advantageous in multiple other ways. For instance, there is a higher chance that recording sites are physically located near individual neurons [4]. Furthermore, several studies showed that a higher single unit yield can be achieved with a higher electrode density [5], and that a considerable number of pyramidal cells fire spikes with a larger spatial spread than interneurons [6]. Thus, the spikes of several small interneurons located in the vicinity of neural probes having a low electrode density might not be recorded, resulting in a biased pyramidal cell – interneuron ratio. High electrode coverage and increased electrode density might also provide other benefits, including, for instance, the compensation for electrode drift or a more accurate separation of overlapping spike waveforms [7]. However, using an electrode pitch below 4  $\mu m$  will not lead to any further improvement in terms of being close to neuronal signal sources [4].

Usually one of the first analysis methods which is applied on the recorded spiking activity data is spike sorting, which is used in many fields of basic neuroscience research (e.g. to study the dynamics of neural networks [8]). The identification of

2.2 Related Works 7

spikes of individual neurons is of great importance in some real-time clinical applications as well (e.g. neuroprosthetic devices, brain-machine interfaces [9]). Usually, the first step in a spike sorting algorithms is the detection of spikes, which can be computationally intensive [10].

The performance of current spike detection methods is challenged by multi-channel neural data recorded with high-density, high-channel count silicon probes developed recently [11]. High-density neural probes with closely-packed recording sites can detect the spikes of the same neuron simultaneously on multiple, adjacent sites [12, 13]. In contrast, most spike sorting algorithms are prepared to process data recorded with only a few (usually four) electrodes.

Simple detection methods like amplitude thresholding can offset the detection towards neurons with high amplitude spikes. There are more robust detection methods, like Non-linear Energy Operator (NEO), which has great accuracy, but the number of falsely detected spikes can also impact the performance [14]. Therefore with the help of dedicated equipment e.g. FPGA, GPU or ASIC, the detection of spikes can be made real-time.

Other challenge is the validation of the spike sorting, because not even the highly experienced neuroscientists can annotate the recorded neural data with 100% accuracy. Therefore using a hand-annotated ground truth dataset can produce a deceptive validation result. Neurophysiological signal synthesis can be an important part of spike sorting to produce a reliable ground truth dataset and use it for automatic validation [15].

#### 2.2 Related Works

In the literature of spike detection and neurophysiological signal synthesis many solutions can be seen. In the following various widely used methods are presented.

#### Spike detection

In [16] an analog template matching based spike detection is proposed, using 8 template points in a spike form discriminator called SPIFODIS. Even for very low Signal-to-Noise Ratio (SNR) values the error rate of the algorithm was 50%-15%. In multi-unit neural signals SPIFODIS can reliably isolate spikes, even when action potentials have equal amplitudes.

The authors of [17] combined wavelet transforms with basic detection theory to develop an unsupervised method for robustly detecting and localizing spikes in noisy neural recordings. The authors presented an extensive Monte Carlo simulation, based on actual extracellular recordings and demonstrated that false positive rate of

the algorithm is better than the false positive rates of the amplitude thresholding method or the power detection method.

An optimized amplitude threshold technique to detect the spikes in signals is proposed in [18] using Haar Wavelet to remove the noise, then a morphological filter to detect the spikes. The morphological filter utilizes hybrid GAPSO (Genetic Algorithm-Particle Swarm Optimization) technique to select the optimal structuring element. The optimized amplitude threshold techniques exploited Improved Particle swarm Optimization (IPSO) which is based on fractional velocity, which was implemented in Matlab and capable of achieving 71% average precision rate.

In [19] a template matching based detection algorithm is described that only requires the user to specify the minimum and maximum firing rates of the neurons. It is capable of achieving an accuracy of 90% with a false positive rate of 5 Hz in recordings with an estimated SNR of 3 dB using real recordings with added background noise taken from other recordings.

The authors of [20] presented two approaches for spike detection. First the ensemble empirical mode decomposition (EEMD) is used, then the Hilbert transform is utilized as a pre-processing step to achieve 100% accuracy and very low (4%) false positive ratio wit varying SNR. The second uses fuzzy and probability theories to combine a number of spike detectors to achieve also 100% accuracy and (5%) false positive ratio.

In [21] a genetic algorithm (GA) based method is proposed using the non-linear energy operator (NEO), which utilizes a GA to adjust the threshold value of the NEO technique. The method can recognize the number and the location of action potentials in a neural signal. The authors showed that the genetic algorithm gives better results than selecting the threshold manually and achieves an average accuracy of 86% with a low false positive rate testing on altogether 15 spikes with varying noise levels.

#### Neurophysiological signal synthesis

There are several methods to obtain "ground truth" datasets for spike sorting efficiency validation. Simultaneous paired recordings collecting the spikes of the same neuron both extracellularly and intracellularly would be the most optimal solution, however, this method is technically challenging, therefore the availability of such datasets are limited [22]. Simulating the activity of biophysically realistic neural networks is also an option [23], but the generation of synthesized multi-channel datasets needs high computational power provided only by computer clusters. Finally, "hybrid ground truth" datasets can be generated by using the mean spike waveforms of a subset of well-separated units isolated from real extracellular recordings as templates or donors and add these spike templates at random times and positions of simulated or real recordings [24, 25].

# 2.3 Overall system architecture

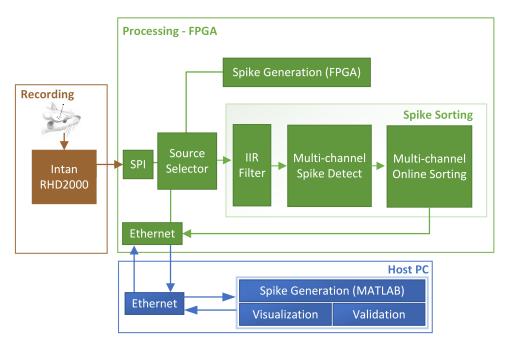

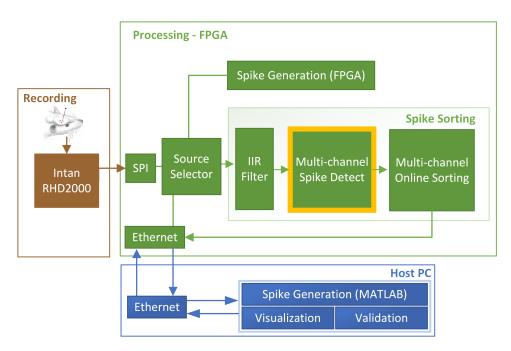

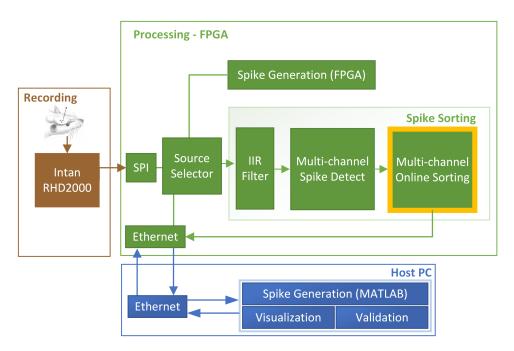

**Figure 2.2:** *Schematic diagram of the proposed spike sorting system.*

The overall system is presented in the actual Chapter, because it is necessary for the better understanding of the connections between the detection and synthesis parts detailed in this Chapter. The overall system information is also relevant in Chapter 3, where the classification part is detailed.

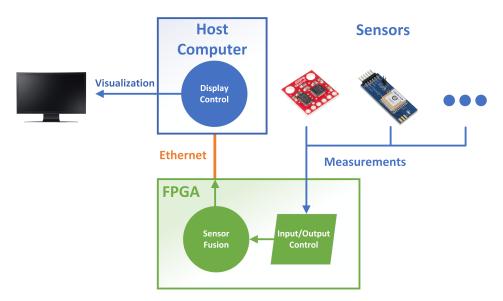

The schematic diagram of the proposed spike sorting system can be seen in Fig. 2.2. The proposed system can be split into three main blocks, the *Recording*, the *Processing* and the *Host PC*, which can be seen in Fig. 3.1. The *Recording* block contains an *Intan RHD2000* electrophysiological recording system. The *Processing* block can be further divided into the *Ethernet* interface, *SPI* interface, Pre-processing *IIR Filter* module, *Spike Generation (FGPA)* (see Section 2.4) module and the *Spike Sorting* module, which contains the *Multi-channel Spike Detect* (see Section 2.6) and the *Multi-channel Online Sorting* (see Section 3.3) cores. The *Host PC* block includes the *Ethernet* interface, the *Visualization* module, the *Spike Generation* module, and the *Validation* module.

The proposed system is able to process in vivo neural measurement acquired by the Intan RHD2000 (Intan Technologies, Los Angeles, CA, USA) board, as well as simulated neural recordings generated by the *Spike Generation* module on the *Host PC*. The path of the incoming neural data can be selected in case of *in vivo* (online), stored data (offline) or simulated operations. The selection is made using the *Source Selector* block, which handles the incoming data based on the configuration, which

can be altered using the switches on the FPGA board.

#### 2.3.1 Electrophysiological Recording

The proposed system was designed to process neural data recorded with a 128-channel high-density silicon-based probe  $(50\mu m \times 100\mu m)$  comprising closely-packed electrodes  $(20~\mu m \times 20\mu m)$  arranged in a  $32\times 4$  array with a center-to-center electrode distance of  $22.5\mu m$  [26]. Measurements of wideband brain signals (0.1-7500~Hz) with this type of probe were obtained with the Intan RHD2000 electrophysiological recording system at 20 kHz sampling frequency/channel and with 16 bit resolution. These 128-channel recordings usually contain hundreds of thousands of spikes fired by dozens of neurons during a time period of one hour. The Intan RHD2000 uses the SPI protocol for communication purposes.

#### 2.3.2 Pre-processing IIR Filter

The high-density bioelectrical activity recorded from the brain tissue can be separated into local field potentials (below 500 Hz) and spiking activity (500-5000 Hz). Therefore the recorded wideband data should be filtered before spike sorting. In the proposed system a Butterworth Infinite Impulse Response (IIR) third-order zero-phase band-pass filter is used to extract the spiking activity.

The filter can be implemented as two Finite Impulse Response (FIR) filters combined together based on Direct Form I structure with seven 18 bit coefficients in each filter. The FPGA resource requirement of the pre-processing IIR filter on 128-channels is only one 36k BRAM and one DSP slice.

## 2.3.3 Processing - FPGA

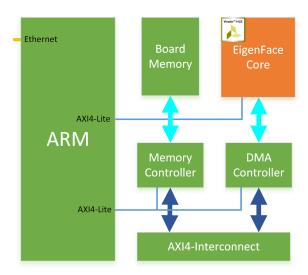

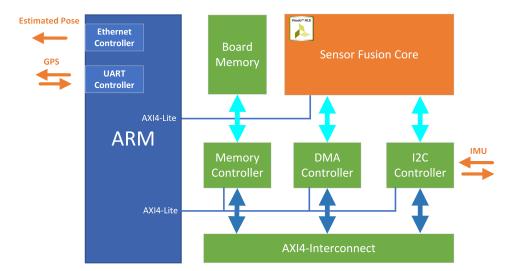

The proposed system was implemented on ZCU106 FPGA board [27], which has a special Xilinx architecture called Zynq, which contains a traditional Programmable Logic (PL) and a Processing System (PS). The latter is an ARM-Cortex processor with various I/O interfaces to connect the system to the outside world. The Gigabit Ethernet interface is used to communicate with the *Host PC* and the SPI interface is used to receive data from the Intan RHD2000 device. The ARM PS communicates with the PL on AXI4 buses (AXI4-Lite, AXI4-Stream, AXI4).

#### 2.3.4 Host PC

The task of the Host PC (Intel Core i7-4770 CPU at 3.4 GHz, 8 GB DDR3 RAM) is to visualize the results of the spike sorting, when in vivo neural recordings are used, and

to validate the sorting algorithm using hybrid ground truth neural data generation, when the signal generator is operating.

# 2.4 Neural Signal Generator

Developing an FPGA-based solution to accelerate the clustering of spikes detected in high-channel count neural recordings is pointless without knowing the spike sorting efficiency. It is a crucial step of the development to validate the performance of the sorting algorithm. This can be achieved by using "ground truth" datasets where the exact time of spikes fired by different single units are known. The "hybrid ground truth" method is chosen and a multi-channel hybrid ground truth dataset can be synthesized using an FPGA board for real-time usage or MATLAB for offline validation. These datasets are used for the validation of the proposed FPGA-based detecting and clustering algorithms (see Section 2.6 and Section 3.3).

#### 2.4.1 Spike Generation Requirements

In order to generate realistic neural data (spikes) many requirements have to be fulfilled. The absolute refractory period of a neuron is 1-2 milliseconds long, during this period the neuron is not able to generate spikes, and the interspike intervals of a neuron have a log-normal distribution [28]. Therefore, a log-normally distributed random number generator should be applied. Furthermore, it was found that the spike-amplitude decays as  $(1/r)^n$  with 1 <= n <= 2 close to soma and n >= 2 far away, where r corresponds to the distance of the electrode from the recorded neuron. Based on this decay and on a 128-channel model probe, where the electrodes are arranged in a  $32 \times 4$  matrix shape with an electrode pitch of 20  $\mu m$ , the action potential of an average neuron can be detected at most six electrodes (120  $\mu m$ ) away from the center, where the spike can be recorded with the highest amplitude [29]. Finally, in the first approach, noise with uniform distribution was added to the generated data.

In addition to these requirements, real-time multi-channel spike generation is required to test the multi-channel Online Sorting architecture (Section 3.3) where the main parameters like the number of neurons, the number of channels and the size of the inter-channel action potential spreading should be configurable.

The sampling rate of the real measurement system where the OSort architecture will be used is 20 kHz, therefore in this case real-time means that the spike generator should produce a sample on all channels with at least 20 kHz frequency.

#### 2.4.2 Mersenne Twister Random Number Generator

To generate the neural dataset, uniform and log-normal distributed random number generation is required. In the literature various uniform random number generation methods can be found. The pseudo-random Mersenne Twister (MT) algorithm is chosen, which can provide an astronomical period of  $2^{19937}-1$  and 623-dimensional equidistribution up to 32-bit accuracy. Furthermore, it passes several statistical tests, including diehard. The algorithm is based on polynomial calculations over the two-element field and uses a twisted generalised feedback shift register with the help of a tempering matrix. The pseudo code and the detailed description of the algorithm can be found in [30].

A continuous probability distribution of a randomly generated variable, which logarithm is normally distributed, is called log-normal distribution. The log-normally distributed random number generation is based on the output of the MT algorithm normalized into the (0,1] interval. The inverse transform sampling method can be used to generate random numbers from any probability distribution, if the cumulative distribution function (CDF) is known and invertible. The CDF of the log-normal distribution can be written as follows:

$$\frac{1}{2} + \frac{1}{2}\operatorname{erf}\left[\frac{\ln x - \mu}{\sqrt{2}\sigma}\right],\tag{2.1}$$

where x is the probability variable,  $\mu$  is the mean,  $\sigma$  is the variance, and erf is the error function, which can be written as follows:

$$\frac{1}{\sqrt{\pi}} \int_{-x}^{x} e^{-t^2} dt,$$

(2.2)

and erf(x) describes the probability of a random variable X falling in the range [-x,x]. Inverting the log-normal CDF, the quantile function can be given by:

$$e^{\mu + \sigma \Phi^{-1}(p)}, \tag{2.3}$$

where p is a uniformly distributed random number in the range of (0,1], and  $\Phi^{-1}$  is the inverse error function, which can be approximated using a Maclaurin series as follows:

$$\sqrt{\pi}(\frac{1}{2}z + \frac{\pi}{24}z^3 + \frac{7\pi^2}{960}z^5 + \frac{127\pi^3}{80640}z^7...),$$

(2.4)

where z is an uniformly distributed random number in the range of (-1, 1).

#### 2.4.3 FPGA architecture

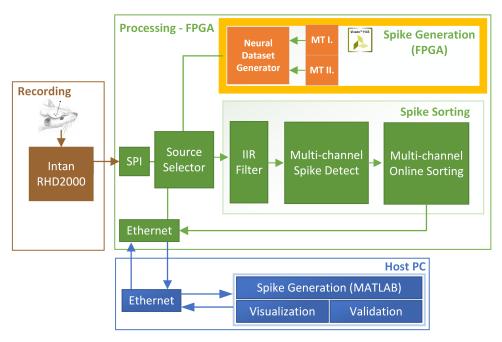

In Fig 2.3 the schematic diagram of the proposed spike sorting system can be seen, where the Spike Generation (FGPA) part is emphasized and detailed.

**Figure 2.3:** Schematic diagram of the proposed spike sorting system. The Spike Generation (FGPA) part is emphasized and detailed.

The Spike Generation contains two main parts: the *Mersenne Twister* (MT I. and MT II.) cores, and the *Neural Dataset Generator* core. The *Mersenne Twister* cores are responsible for the generation of random numbers used in the inverse transform sampling to compute the log-normal distribution of interspike intervals (*Mersenne Twister I.* core) and the noise generation (*Mersenne Twister II.* core).

The FPGA implementation of the log-normally distributed random number generator is done, however the *ARM Processing System (PS)*, which is a dedicated CPU on the FPGA board has enough computation performance to complete this task. In this way, the log-normal random number calculation does not occupy any FPGA resources.

The ARM (PS) also handles the communication (SPI, Ethernet) and the DDR memory access through DMAs.

#### Mersenne Twister

The Mersenne Twister I core calculates the random numbers required in inverse transform sampling to generate log-normally distributed firing times. The Mersenne Twister II core is responsible for the generation of the noise.

These cores are based on the pseudo-code and parameters published in [30], but some modifications were required to achieve optimal performance during the FPGA implementation. The initialization phase of the algorithm is not changed, but the twist and the output generation is separated, since only the output generation can be pipelined. Using this modified algorithm the twist step can be performed in 1872 clock cycles, when N is 624. After this initialization period is completed a new random number can be generated in each clock cycle. The twist step is called after generating 624 random numbers.

#### **Neural Dataset Generator core**

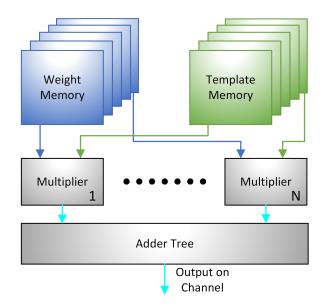

**Figure 2.4:** *Schematic diagram of the output generation for one channel*

The *Neural Dataset Generator* core generates the multi-channel neural dataset. The first part of this process is the simulation of the action potential spreading through the neighbouring 6 channels. This is based on a pre-defined normally distributed Gaussian-kernel. The shape of the electrode array is stored in a Look Up Table (LUT), which is used for proper indexing of the weight matrix. For each channel and each neuron, the weight matrix contains the corresponding spreading weight value from the Gaussian-kernel. The electrode array LUT and the weight matrix is pre-calculated on the *ARM PS*. Therefore, the generation of one output sample is a simple multiplication between the weight coefficient of the actual channel and the value of the actual spike template. Finally, an adder tree summarizes the weighted template values and the result will be the output of one channel at one time. The architecture of the *Neural Dataset Generator* core can be seen in Fig. 2.4.

Another important part of the dataset generation is to set up the log-normally distributed intra-channel spike firing distances for each individual neuron. On the *ARM PS* the generated log-normally distributed random numbers are sorted in ascending order with the corresponding neuron values and stored in a structure. This firing structure contains the firing time and the identification number of the firing neuron.

To generate the final multi-channel dataset, the *Neural Dataset Generator* core reads the neuron identification value from the firing time structure and enables that neuron to fire at the corresponding time stamp. The next fire time will be read in the next clock cycle. When all neurons are enabled to fire, then the *Neural Dataset Generator core* pauses the reading.

The *Spike Sorting* part processes the data from the electrode by channel, so the core gets one channel sample per clock cycle. Therefore the *Neural Dataset Generator* core should work in the same fashion.

|                     | P    | vailabl           | e resourc  |        |  |  |

|---------------------|------|-------------------|------------|--------|--|--|

|                     | BRAM | DSP               | FF         | LUT    |  |  |

|                     | 102  | 120               | 12,150     | 14,034 |  |  |

|                     |      | Device            | Utilizatio | n      |  |  |

|                     | BRAM | DSP               | FF         | LUT    |  |  |

| Mersenne Twister x2 | 1%   | 7%                | 1%         | 4%     |  |  |

| Log-normal (ARM)    | 4%   | 20%               | 3%         | 11%    |  |  |

| Neural Signal       | 7%   | 34%               | 6%         | 25%    |  |  |

| Generator           | / 70 | 3 <del>4</del> %0 | 0%0        | 23%    |  |  |

| Summarized          | 8%   | 41%               | 7%         | 29%    |  |  |

**Table 2.1:** Area requirements and device utilization of the synthesized modules

## 2.4.4 Implementation Results

The proposed *Mersenne Twister* and *Neural Spike Generator* cores (Signal Generation subsystem) are developed and synthesized using the Vivado High Level Synthesis (HLS) version 2016.4. The spike generation architecture is synthesized to a ZedBoard equipped with a Zynq-7020 FPGA. The available resources on the Zynq-7020 and the resource requirements of the cores can be seen in Table 2.1.

During the development, the FPGA and the ARM-based implementation of the *Log-normal* core were tested. Since the *ARM PS* is capable to generate log-normally distributed random numbers in 150 FPGA clock cycles, the ARM PS was chosen for this calculation. In this case this core does not require any FPGA Programmable Logic resources.

|                  |             | Latency  | Iteration | Trip Count |

|------------------|-------------|----------|-----------|------------|

|                  |             | Latericy | Latency   | Trip Count |

| Mersenne         | init        | 5607     | 9         | 623        |

| Twister          | twist       | 1872     | 3         | 624        |

|                  | output_gen  | 625      | 3         | 624        |

|                  | init        | 57       | 27        | 32         |

| Log-normal (ARM) | maclaurin   | 140      | 14        | 128        |

|                  | output_gen  | 65       | 25        | 32         |

| Neural Signal    | dataset_gen | 2560026  | 28        | 256000     |

| Generator        | uataset_gen | 2300020  | 40        | 230000     |

**Table 2.2:** Detailed Latencies of the Synthesized Cores

If the resource requirement of the multi-channel Spike Detect and Online Sorting (Section 3.3) is added to the resource requirements of the Spike Generation subsystem, the DSP resource utilization is greater than 115%. Therefore, the Log-normal core can not be implemented on the Zynq-7020 FPGA, so it is important to move this computation to the *ARM PS*.

After the Vivado HLS synthesis, the latencies of the cores can be seen in Table 2.2. In the case of the Mersenne Twister core, the twist step requires 1872 clock cycles, while the output generation requires 624 of it. So, 1872 + 624 = 2496 clock cycles are needed to generate 624 random numbers. Therefore, an average of 4 clock cycles are required to generate one random number. The Log-normal core running on the ARM PS requires 150 clock cycle latency to generate one log-normal value. The spike generation is performed in one second windows using the Neural Signal Generator core. This core requires only one clock cycle to generate one sample on all 128 channels. Before the first window, a proper initialization is required. This initialization consists of the electrode array LUT, the weight matrix, the random number and the log-normal number generation. These calculations are performed by the ARM PS, except the random number generation, which is done by the Mersenne Twister II. core. During the generation of the channel samples of the next windows, only the log-normal number generation is required, which can be performed parallel to the previous window. The clock frequency of the Zynq-7020 on the ZedBoard is 100 MHz, so the generation of the channel samples can reach and even exceed the necessary 20 kHz sampling rates.

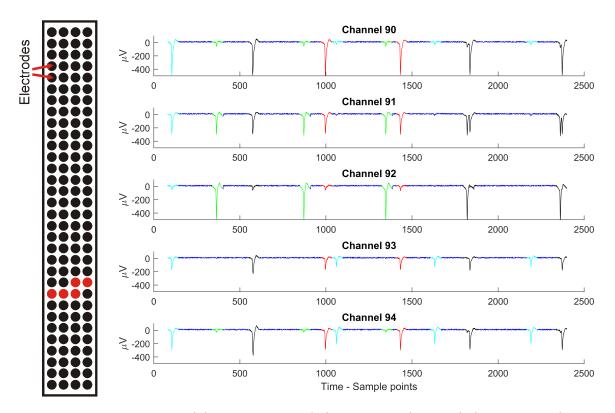

In Fig. 2.5 the results of the dataset generation can be seen on 5 adjacent channels with 3 firing neurons in a 0.1 second window, where the inter-channel signal spreading can be observed. The spikes are grouped by the firing neurons, each neuron has a unique color, while multi-unit spikes have black color.

**Figure 2.5:** A 0.1 second long segment of the generated neural data on 5 adjacent channels (electrodes corresponding to the channels are indicated on the left side with red circles on the schematic image of the model probe). The spikes of the three different neurons are highlighted in different colors.

#### 2.4.5 Conclusion

A real-time multi-channel hybrid ground truth neural dataset generator is presented using a Zynq-7020 FPGA. The results show that the presented architecture can be implemented on the Zynq-7020 FPGA with 100 MHz clock frequency and it is capable of generating multi-channel neural samples at every clock cycle. The neural dataset generator are used for the validation of the spike sorting architecture. Another purpose of the proposed neural spike generator could be the pre-calibration or pre-teaching of the spike sorting architecture.

# 2.5 Comparison of spike detection algorithms

In Fig. 2.6 a conventional spike sorting system can be seen, where the spike detection step is highlighted. In a conventional spike sorting system the electrical signal from the neural probe is converted to a digital signal first, then a bandpass filter is applied to reduce noise, because the action potentials are often in the 300 Hz - 3000 Hz fre-

**Figure 2.6:** Structure of a conventional spike sorting system

quency range. The spike detection step is applied after the filtering, then the features are extracted from the detected spikes. Based on the features the classification can be done [31].

There are several simple spike detection method, which offers easy implementation, but reliable accuracy. These are the NEO, the power method, the positive, the negative, and the absolute amplitude thresholding. Spike detection methods, which based on creating an intermediate signal often suffers from creating a lag between the detection and the input signal. A realign step has to be added to mitigate the lag, which finds the peak of the spike around the detection in a pre-determined window.

### 2.5.1 Non-Linear Energy Operator

The Non-Linear Energy Operator is widely used for spike detection. In discrete time the  $\Psi$  operator can be defined as follows:

$$\Psi[x(n)] = x^{2}(n) - x(n+1)x(n-1)$$

(2.5)

The NEO signal is high only when the input signal is high in power ( $x^2$  is high) and also high in frequency (x[n] value is big, while x[n+1], x[n-1] is small). Action potentials are often characterized as instant impulses, therefore this method has an advantage [32].

The acquired NEO signal is thresholded with an automatically calculated threshold value  $T_{NEO}$ .

$$T_{\text{NEO}} = C_{\text{NEO}} \frac{1}{N} \sum_{n=1}^{N} \Psi[x(n)]$$

(2.6)

where N is the number of samples, and  $C_{NEO}$  is the scaling factor, which is adjusted by experiment for every signal type [33].

#### 2.5.2 Power Method

The standard deviation is computed of the signal using a sliding window as the power signal. Then the mean and the standard deviation of this signal is computed, finally the power signal is thresholded with an automatically calculated threshold value

from the standard deviation and the baseline mean. The power signal is calculated as follows.

$$s[n,m] = \sqrt{\frac{\sum_{i=n}^{m} (x_i - \bar{x}[n,m])^2}{i-1}}$$

(2.7)

where s[n,m] is the sliding standard deviation and  $\bar{x}[n,m]$  is the sliding mean between n and m samples. The used kernel size in this case is 18 samples, which is a typical spike width (0.9ms) at 20 kHz sampling rate). The sliding mean is defined as follows.

$$\bar{x}[n,m] = \frac{\sum_{i=n}^{m} x_i}{m}$$

(2.8)

where  $\bar{x}[n,m]$  the average value of the input signal between the n and m samples. The automatic threshold value  $T_P$  is calculated as follows.

$$T_P = \bar{s} + C_P \sqrt{\frac{\sum_{i=1}^{N} (s_i - \bar{s})^2}{N - 1}}$$

(2.9)

where  $\bar{s}$  is the mean value of the power signal, N is the number of samples and  $C_P$  is the scaling factor [34].

# 2.5.3 Amplitude Thresholding (Positive, Negative, Absolute)

The simplest spike detection algorithms are the amplitude thresholding methods. There are 3 different approaches, where the signal, which is being thresholded are different:

- Positive Uses the signal without modification

- Negative Negates the signal

- Absolute Uses the absolute value of the signal

The automatically calculated threshold value  $T_{AMP}$  is defined as follows.

$$T_{\text{AMP}} = C_{\text{AMP}} \frac{median(|x|)}{0.6745} \tag{2.10}$$

where x is the input signal, and  $C_{\text{AMP}}$  is the scaling factor. The 0.6745 denominator value is based on the assumption that the noise in the signal has a normal distribution, therefore the denominator is the inverse of the cumulative distribution function (CDF) of the standard normal distribution at 0.75 [35].

#### 2.5.4 Cross-Correlation Based Spike Detection

Using correlation for template-matching is a usual approach, although in neural activity detection is rarely used due to the base template requirement. A cross-correlation based spike detection implementation is proposed with pre-defined average templates, which requires an expert neuroscientist who is capable of selecting spikes in a pre-recorded signal. With this a priori knowledge the average template will be similar to the spikes in the actual recording, therefore the cross-correlation can be effective. The cross-correlation  $R_{xy}$  is calculated as follows.

$$R_{xy}[k] = \sum_{-\infty}^{\infty} x[m]y[m-k], -\infty \le k \le \infty$$

(2.11)

where x is the average template and y is the signal.

A normalization step is required, so the results will be in the [0,1] range, which calculated as follows.

$$\hat{R}_{xy} = \frac{R_{xy}}{max(|R_{xy}|)} \tag{2.12}$$

where  $\hat{R}_{xy}$  is the normalized cross-correlation. After the normalization the spikes are extracted by a threshold  $T_{XCorr}$  on the resulting signal.

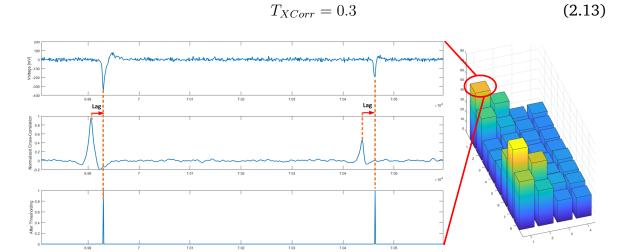

**Figure 2.7:** Cross-correlation based spike detection, visualization on channel 1. From top to bottom: generated neural (3 neurons) signal, normalized cross-correlation, results of thresholding and realign. The generated neural signal on the 4x8 electrode array can be seen on the right

In Fig. 2.7 the cross-correlation based spike detection can be seen, with the generated neural signal on  $4 \times 8$  electrode array.

Without the right quality templates, the proposed method is not suitable for realtime spike detection, but it can be a good candidate for re-detecting and re-classifying an already partially classified recording.

#### 2.5.5 Evaluation

The comparison between different spike detection methods are evaluated using the known spike times from the template based neural signal generator (see Section 2.4) using MATLAB. The neural signal generator is capable of generating a maximum channel number of 128, but it is reduced to 32 channels  $(4 \times 8)$  in this case. Furthermore it simulates the inter-channel action potential flow with a gaussian kernel, uses a random firing frequency for each neuron and the noise level is variable.

The signal generator has been set to iteratively generate 4 dB - 10 dB SNR signals with 3-12 neurons, for each iteration all of the detection methods has been evaluated, altogether on 90 combination.

The SNR is calculated as follows.

$$SNR = 10 \log_{10} \frac{Energy \text{ of Signal}}{Energy \text{ of Noise}}$$

(2.14)

One evaluation metric is the true positive ratio (TP), which can be defined as:

$$TP = (\frac{\text{Number of good spikes found}}{\text{Number of spikes}}) \cdot 100$$

(2.15)

Second metric is the false positive ratio (FP), which computed as:

$$FP = \frac{\text{Number of false spikes detected}}{\text{Number of spikes}}$$

(2.16)

**Table 2.3:** Comparison of different spike detection methods, with 12 neurons, 10,7,4 SNR

|             | SNR    |        |        |       |        |       |

|-------------|--------|--------|--------|-------|--------|-------|

| Method      | 10     | dB     | 7 d    | lB    | 4 d    | B     |

|             | TP [%] | FP     | TP [%] | FP    | TP [%] | FP    |

| NEO         | 100    | 50.40  | 100    | 29.15 | 100    | 17.55 |

| Power       | 32.87  | 0.67   | 32.86  | 0.38  | 35.84  | 3.24  |

| AMPP        | 0      | 19.142 | 0      | 8.42  | 0      | 1.79  |

| AMPN        | 100    | 37.97  | 100    | 24.39 | 100    | 18.09 |

| AMPA        | 100    | 58.87  | 100    | 33.97 | 100    | 21.03 |

| Cross-Corr. | 99.41  | 0.53   | 96.63  | 0.53  | 92.47  | 0.52  |

#### 2.5.6 Results and Conclusion

The results are summarized in Table 2.3, which contains the results for 12 neurons on 32 channels with varied 4, 7, 10 dB SNR. It can be seen, that the AMPP method unfortunately cannot hit any good spike, only false. It is an expected outcome, due to the generated signal only contains spikes, which are in the negative region.

The NEO, AMPN and AMPA methods are very accurate even at low SNR value, but have a high false positive ratio. The NEO spike detection found 50 times more spikes than the true spikes in the signal. In the case of the NEO it can be seen, that the false positive ratio is decreasing as the SNR increasing, which can be explained with the threshold computation of the NEO. The Power spike detection method has a low accuracy, but also a low false positive ratio.

However the proposed cross-correlation based method maintains accuracy over 90% and the false positive ratio is at a maximal value of 0.53.

It can be concluded, that the cross-correlation based method has lower accuracy, then the NEO, AMPN or AMPA, but has a far lower false positive ratio, but NEO do not requires stored templates and false positives are decreasing as the noise increases, which makes NEO a good candidate for FPGA implementation.

# 2.6 Multi-channel Spike Detection

**Figure 2.8:** Schematic diagram of the proposed spike sorting system. The Multi-channel Spike Detect part is emphasized.

Single-channel spike detection is easier, because there are no adjacent electrodes, therefore overlapping (multi-unit) spikes are less likely to appear and the number of active cells are small. On the other hand, using closely packed electrodes the number of cells are proportionally increasing with the number of channels and also the structure of the electrode array is important. A new source of information appears, which is the spatial component. The action potential of a firing neuron propagates through the electrodes with decreasing amplitude in all direction. The spatial information can point towards the source of the action potential to the channel with the highest action potential amplitude.

In Fig. 2.8 the schematic diagram of the schematic diagram of the proposed spike sorting system can be seen. The Multi-channel Spike Detect part is emphasized and it is detailed in this Section.

# 2.6.1 Spike Detection Algorithm

In the FPGA architecture the spike detection part is called *Multi-channel Spike Detect* core, which is responsible for the real-time multi-channel spike detection. In the proposed system the Non-Linear Energy Operator (NEO) is used for spike detection, because it is the most efficient among the commonly used spike detection methods and it is easily implementable on FPGA devices [35, 36, 37].

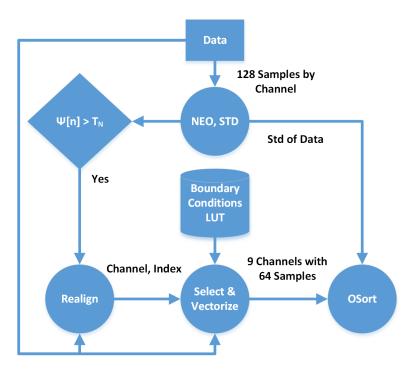

Figure 2.9: Flow diagram of the NEO based spike detection algorithm

The flow diagram of the spike detection algorithm can be seen in Fig. 2.9. In this

case one sample from each of the 128 channels is fed into the NEO and the standard deviation (STD) calculation block. The STD value is used later in the spatial window-based OSort module to calculate the automatic clustering and merging thresholds. When the  $\Psi[x(n)]$  NEO value is larger than the automatically calculated  $T_N$  threshold, then the peak of a spike is detected. Afterwards, a temporal window around the detected peak on the actual channel is checked by the realign method, that the peak of the spike is certainly in the center of this temporal window. The correct alignment is crucial, because the comparison can not be done correctly with unaligned spikes, resulting in compromised classification.

In an electrode array with closely-spaced recording sites the spike waveform of a neuron spreads through adjacent sites, which also has to be considered for detection. After the realignment of the temporal spike window, a spatial window of  $3\times 3$  electrodes is examined around the firing channel at the aligned spike position to determine the source of the activity. The channel with a higher absolute amplitude in the neighbourhood will be the new center of origin, assuming that electrode is possibly located the closest to the soma of the neuron. Using this method the source channel of the unit activity can be found, eliminating the effect of the multiple detection of the same spike. In case of two or more neurons firing in the spatial vicinity of each other (8-connected or 8-neighbour) the detected spike matrix will be an overlapping spike waveform and will be removed in the merge phase of the classification process. Recording sites on the edges of the electrode array will also detect spikes. In this

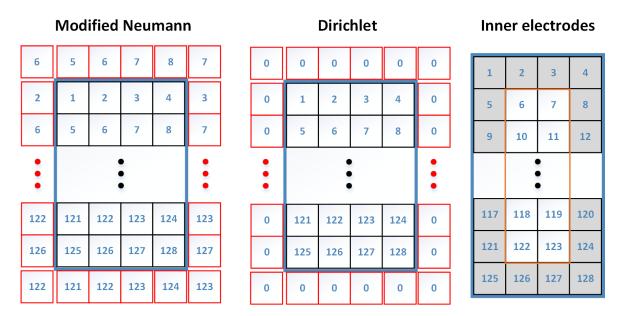

**Figure 2.10:** Possible boundary conditions for the 32 x 4 electrode array configuration, which is stored in the LUT. The recording sites of the electrode array are within the blue rectangle.)

case an incomplete electrode window is selected, because there is no measurement beyond the edges of the electrode array. There are three possible solutions to deal with this issue, which can also be seen in Fig. 2.10:

- *Modified Neumann* The boundary is filled with data of the neighbouring channels, considering a Gaussian distributional cross-talk between the channels.

- *Dirichlet* The boundary is filled with fixed constants, in this case zeros.

- *Inner electrodes* Only the inner electrodes are used for detection, therefore spike sorting is limited in this case.

The realign method specifies the origin of the activity and the precise alignment, so a spike matrix containing the data of 9 channels is selected from the electrode array and sent to classification. In the proposed system the *Modified Neumann* boundary condition is used.

#### 2.6.2 FPGA Architecture of Spike Detection

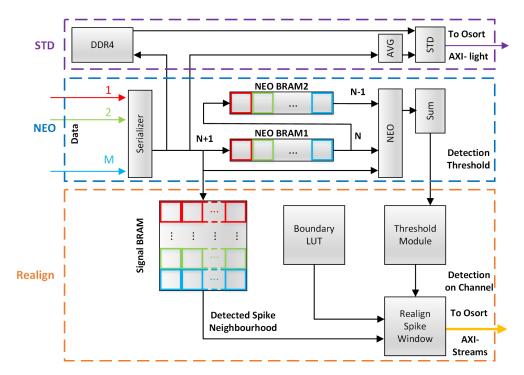

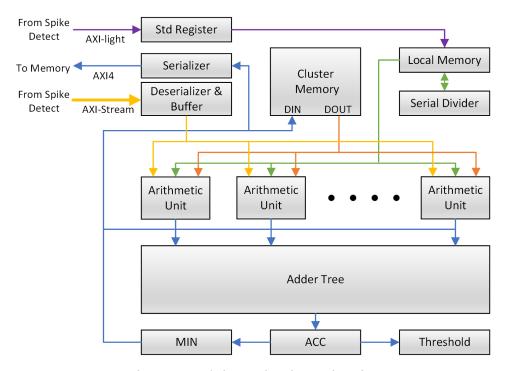

The *Multi-channel Spike Detect* architecture can be split into the STD, the NEO and the Realign computation parts, which can be seen in Fig. 2.11. The signal is sampled at 20~kHz with 128 channels in the proposed system.

**Figure 2.11:** The architecture diagram of the detection

The STD computational part is responsible for computing the standard deviation value of the incoming signal using a five seconds window, which contains  $100000 \times 128$  samples. There is not enough memory for this on the FPGA, therefore the off-chip DDR4 memory is used to store the samples. The average computation can be done continuously in the AVG block, while the subtraction and power operations are done in the STD block. In the NEO computation part the spike detection with Eq. 2.5 and the threshold calculation using Eq. 2.6 is done. The NEO signal can be calculated parallel for each channel using the NEO BRAM1, BRAM2 and the Serializer as N-1, N and N+1 inputs.

In this implementation the value of  $c_N$  and N are both 2 (determined experimentally), so the  $T_N$  NEO threshold value calculation can be reduced to a simple accumulation. At the first 2 samples the system is not operating, this can be considered as an initialization phase.

The Realign part of the *Multi-channel Spike Detect* is responsible for the following:

- Alignment of the detected spikes in the spike window;

- Determination of the channel containing the maximal amplitude spike in the neighbourhood around the detection;

- The appropriate selection of the  $3 \times 3$  channels on the electrode array.

The Realign part uses the Signal BRAM, which can store 80 samples for each (128) channel. A spike is 64 samples wide, but the detection is not precise, so 16 more samples are stored, altogether 80. The Threshold Module compares the actual NEO value on each channel with this detection threshold value and when it is lower than the actual NEO value, then a spike is detected. Detection events for the channels are stored in a 128 wide vector. If a detection occurs, then the detection event flag for the actual channel is switched, which indicates that 40 samples later the Signal BRAM will contain the full spike for that channel and can be used for realignment. The Realign Spike Window block uses the absolute value of the spike in the temporal window from the Signal BRAM to find the maximal point for the alignment.

Afterwards, the neighbourhood of the detected spike at the alignment point is extracted from the Signal BRAM, and searched for the maximal value in that  $3 \times 3$  electrode window. Using this method the channel with the maximal amplitude will be in the center of the electrode window, which is crucial for the effectiveness of the comparison performed in the *Window-based Online Sorting* core later. If the channel is at the border of the electrode array, and the spatial window is out of this border, then with the help of the Boundary Look Up Table (BLUT), the  $3 \times 3$  spatial window can be prepared and sent to classification using AXI-Streams, 9 streams parallel for each channel.

#### 2.6.3 Results and Discussion

**Table 2.4:** Area requirements and device utilization of the synthesized multi-channel spike detection architecture

|      | Utilization | %      |

|------|-------------|--------|

| FF   | 10915       | 2.36%  |

| LUT  | 42692       | 18.52% |

| DSP  | 6           | 0.35%  |

| BRAM | 7           | 1.12%  |

**Table 2.5:** Detailed latency of the multi-channel spike detect architecture

|              | Latency(clock cycles) | Trip Count(clock cycles) |

|--------------|-----------------------|--------------------------|

| Load Channel | 129                   | 128                      |

| NEO          | 131                   | 128                      |

| Realign      | 163                   | 154                      |

| Total        | 423                   | 410                      |

| STD          | 12.8 M                | 12.8 M                   |

In Table 2.4 the area requirements and device utilization of the synthesized multichannel spike detection architecture can be seen, which shows that the LUT requirement is the highest with 18%. Based on the detailed latency of the multi-channel spike detect architecture in Table 2.5, it can be concluded that spike detection part can be done in 423 clock cycles, 2.12  $\mu s$  at 200 MHz clock frequency, therefore the proposed multi-channel spike detection architecture can process up to 471 698 spike/s. The STD block is shown in a separated row, because it is required to run independently and does not influence the operation latency of the detection. Table 2.3 shows the efficiencies of several spike detection methods, the NEO is included, which is used in the proposed architecture. The efficiency of the multi-channel spike detection FPGA architecture is very close to the MATLAB simulation, only the fix-point precision and the number representational approximations are different.

For different electrode array configurations different pre-calculated Boundary LUTs could be used, which needs different bit files on the FPGA. The appropriate one must be chosen for the corresponding electrode array and programmed it to the FPGA.

#### 2.7 Discussion and concluding remarks

An FPGA-based multi-channel hybrid template-based multi-channel neural signal generator for the simulation and a multi-channel spike detector using NEO have been developed for the detection of neural signals from closely packed microelectrode arrays. The main challenges with the simulation were the randomness of the activities and the modelling of crosstalk between channels. Also the main importance was to resemble reality as much as possible. The spike detection also posed challenges with the overlapping spikes due to the crosstalk and to find the source channel of a spike "wave". The neural signal synthesis were verified with neuroscientists and the evaluation of the detection showed promising results for real-time usage.

#### 2.8 Contributions

The author of this PhD thesis is responsible for all the contributions presented in this chapter, which include the following main novelties:

- I / 1. I gave a Non-Linear Energy Operator (NEO) based multi-channel action potential detecting FPGA architecture, which also capable of determining the source of the firing neuron in a multi-channel electrode array. I also showed that it can operate in real time.

- I / 2. I proposed a cross-correlation based action potential detection method, showed its efficiency and pointed out its limitations.

- I / 3. I designed a neurophysiological signal generator algorithm, which is capable of placing action potential templates on randomly selected channels with randomly determined frequency and firing crosstalk, taking into account the theory of neuron firing known so far in neuroscience.

- I / 4. I gave an FPGA architecture, which is capable of generating neurophysiological signals using the Mersenne-Twister pseudo-random number generator algorithm. I showed that the architecture can generate real-time neurophysiological signals for an electrode array with 128 channels.

#### Chapter 3

# FPGA-based real-time classification of neurophysiological signals taking into account spatial information

In this chapter the real-time FPGA-based classification of multi-channel neurophysiological signals using also the spatial information from the closely packed microelectrode array is described. An unsupervised single-channel online classification algorithm called Online Sorting (OSort) is chosen for FPGA implementation and modification to handle multi-channel neural signals. The main challenge is to handle the signals coming from a microelectrode array with 128 electrodes sampled with 20 kHz, which means  $2560000 \ samples/s$ .

The classification step is strictly bound to the results of the previous step, the detection. In some methods also a feature extraction step is present, but the OSort algorithm uses the detected spikes as features, also called templates. Therefore in this chapter the results are presented with the detection step, forming together a spike sorting system.

The structure of the chapter is as follows. In Section 3.1 and Section 3.2 the introduction and related works are presented. The detailed description of spatial information based OSort for real-time spike sorting using FPGA can be seen in Section 3.3. The discussion and concluding remarks is presented in Section 3.4. In Section 3.5 the contributions can be seen.

#### 3.1 Introduction

High-channel-count neural probes ([7, 38, 39]) comprising over hundred electrodes are able to record the activity of hundreds of neurons from numerous individual brain positions simultaneously. Spike trains of individual neurons (called single-unit

activity) can be separated from the detected multi-unit activity in the classification step of spike sorting [35].

In basic neuroscience research spike classification or clustering is used during the offline analysis of the recorded neural data as well as in real-time clinical applications (e.g. in brain-machine interfaces to control neuroprosthetic devices [40]). However, using a typical spike sorting solution with general-purpose computers the real-time processing of multi-channel neural data is challenging and can greatly reduce the efficiency of clinical applications designed to provide rapid feedback.

Therefore, real-time clinical applications as well as electrophysiological experiments performed using high-density neural probes could get advantage of hardwareaccelerated clustering of neural recordings. Dedicated systems based on Field-Programmable Gate Arrays (FPGAs) or Application-Specific Integrated Circuits (ASICs) are especially suited for this task because they are small, wearable and use insignificant amount of energy compared to traditional Central Processing Units (CPUs) or Graphics Processing Unit (GPUs). Using a dedicated system the computation time to process the vast amount of data from a multi-channel (high-dimensional) neural recording can be significantly reduced ([41, 42, 43, 44]). Although ASIC chips might be smaller and consume less power compared to FPGAs, which is advantageous in electrophysiological experiments with freely behaving animals where wireless technology is used to transfer neural data from the brain to the recording system [45], they usually lack flexibility for changes. In contrast, design flexibility provided by FPGAs might be in many cases a more important factor than small chip area or low power consumption. For example, electrophysiological recording systems as well as algorithms used for spike classification are subject to extensive research and development, therefore tend to change rapidly.

The high spatial sampling of spikes might allow a more reliable and accurate identification of neurons in case of template matching-based spike sorters. The reason behind this is that neurons located in different positions relative to the electrode array will have at least a slightly different multi-channel spike waveform (investigated for example in a spatial window incorporating  $3 \times 3$  electrodes). Thus, the additional spatial information provided by high-density probes might be exploited to increase the accuracy of the spike sorting process [6].

Therefore, new algorithms using novel approaches and/or implementing the clustering step of spike sorting on dedicated hardware (e.g. Field Programmable Gate Array (FPGA), Application-Specific Integrated Circuits (ASIC), Graphics Processing Unit (GPU)) are under intensive development to reduce the computation time required to process the recorded high-dimensional data [36, 46, 47, 48].

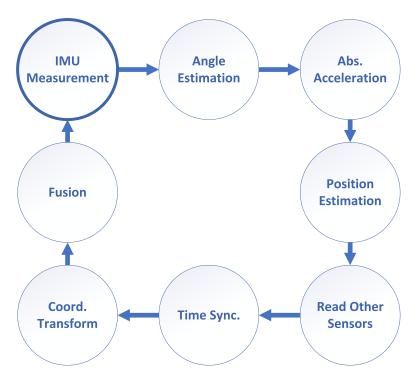

In this work, a window-based spike sorting hardware architecture using Systemon-Chip (SoC) FPGA is presented for real-time processing of high-channel-count neural data recorded with a dense electrode array. The incoming spikes are observed 3.2 Related Works

on each channel in parallel. The sorting part of the proposed system is window-based, because it takes into consideration the spatial information in a window of the electrode array. To perform spike sorting in this window-based manner, the Online Sorting (OSort) algorithm [49] was modified. OSort is an unsupervised template matching algorithm, originally designed to process single-channel recordings. The functionality of the system was verified using the hybrid ground truth signal generator (Section 2.4) and in vivo measurement data [26].

#### 3.2 Related Works

In the literature several FPGA-based solutions can be found, which were developed for spike sorting not suited to process data recorded with high-channel-count neural probes [15, 36, 41, 43, 46, 50], while [44], [51, 52, 53] capable of sorting action potentials recorded with high spatial resolution probes [54, 55]. A detailed comparison to the proposed system is presented in Section 3.3.5.

## 3.3 Spatial information based OSort for real-time spike sorting using FPGA

**Figure 3.1:** Schematic diagram of the proposed spike sorting system. The Multi-channel Online Sorting part is emphasized.

In Fig. 3.1 the schematic diagram of the proposed system can be seen, where the Multi-channel Online Sorting part is emphasized and detailed in this section. The Multi-channel Online Sorting part is based on the proposed spatial window-based Online Sorting algorithm.

#### **Spatial window-based Online Sorting**

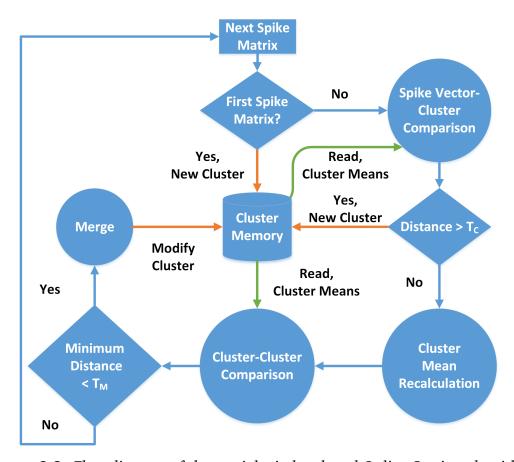

This algorithm extends the original OSort algorithm with a cluster memory, which is required for the optimal FPGA implementation. The flow diagram of the proposed algorithm can be seen in Fig. 3.2.

Figure 3.2: Flow diagram of the spatial window-based Online Sorting algorithm

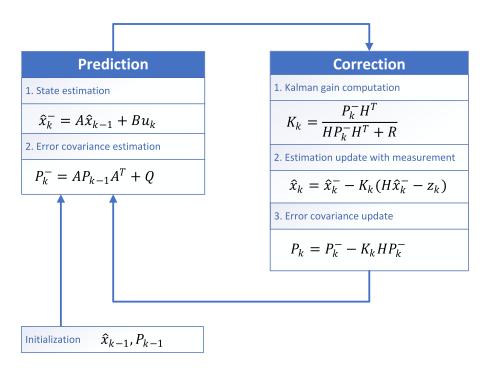

The clustering and cluster merging thresholds ( $T_C$  and  $T_M$  respectively) are automatically determined and adaptively changed during the classification based on the STD value calculated in the spike detection part. The threshold value of one channel is calculated based on the standard deviation of a five seconds long moving window (determined experimentally) from the neural recording (signal) as follows.

$$T_C = T_M = std(signal)^2 \cdot c_C \cdot N_S, \tag{3.1}$$

where  $c_C$  is the clustering correction factor [49], and  $N_S$  is the number of sample points in a spike.

When the Multi-Channel Spike Detect core sends the first spike matrix containing 9 spikes from the  $3 \times 3$  electrode window, it is stored as the first cluster in the cluster memory. The next spike matrix will be compared to the saved cluster mean using squared difference as the distance metric. If this spike matrix is similar to the already saved one, then the calculated distance is below  $T_C$ , so it is assigned to this cluster. If it is not similar, and the distance is above  $T_C$ , then the creation of a new cluster is required. This process is applied to the subsequent incoming spike matrices. After the assignment the mean of this cluster will be updated, because the composition of the cluster is changed. Furthermore, the cluster mean update changes the distance between cluster means, therefore a distance check between clusters is needed. If a distance is below  $T_M$ , then the updated and the closest cluster will be merged together forming a new, larger cluster. In this case the smaller cluster will be removed from the memory, and the spike matrices from the smaller are assigned to the larger cluster.

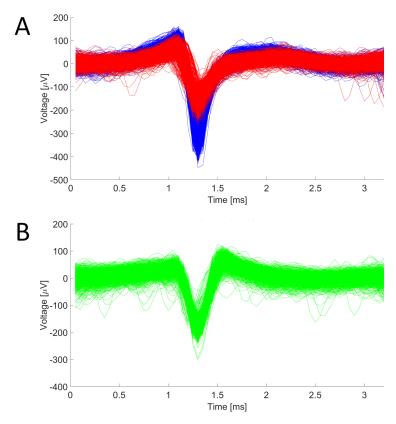

#### Spike Generation

The algorithm and the implementation of the Spike Generation module is fully discussed in Section 2.4. Using ground truth data, the time corresponding to spikes of individual neurons is known and thereby it allows the quantitative assessment of the performance of the spatial window-based OSort spike sorting algorithm. Since in vivo neural data (obtained by direct measurement) and synthetic data (background noise, position and firing time of neurons) were combined to generate the dataset for validation, this is referred to as hybrid ground truth. Spike templates were created from in vivo electrophysiological data recorded with the previously mentioned, 128channel silicon probes from the neocortex of anesthetized rats [26]. The spikes of well-separated units (n = 72) were averaged and the average spike waveforms were used for the construction of templates. Since the high-density probe could record the spikes of a particular unit on multiple, adjacent recording sites, only the recording channel on which the spike appeared with the largest peak-to-peak amplitude was used for template construction. A spike template was represented with 64 sample points/channel (3.2 ms). For a higher variability of spike templates, spike waveforms corresponding to both putative neocortical principal cells (wide spikes, n = 58) and putative neocortical interneurons (narrow spikes, n = 13) were selected [56].

High-density neural probes provide high spatial resolution, that is, the spikes of neurons can be recorded on multiple electrodes simultaneously. The extent of spatial spreading of the spike waveform of a neuron depends on several factors (e.g. neuron-electrode distance, type of the neuron) but is usually a few tens of microns. Therefore, the maximal radius of spatial spreading of a template spike waveforms

was six electrodes (132.5 $\mu m$ ) in each direction with the mean spike waveform located in the center.

To generate a more realistic neural dataset the spatial spread of the spike waveforms of 160 in vivo recorded cortical neurons were examined (obtained with the 128-channel silicon probe used in this study) to extract the spreading patterns. The Spike Generation module (Section 2.4.) was modified based on the found spatial patterns, so in the modified version each simulated neuron has an individual and asymmetrical spike waveform spreading.

#### 3.3.1 FPGA architecture

The *Spike Sorting Module* consists of the *Multi-channel Online Sorting* core and the *Multi-channel Spike Detection* core. The original version of the OSort algorithm [49] works with a single-channel. To process data from a window of the electrode array, the algorithm was modified. The data flow and the structure of the original algorithm are completely redesigned. The neural data are processed in  $3 \times 3$  spatial windows, so the clustering algorithm works on 9 selected channels at a time.

#### **Window-based Online Sorting**

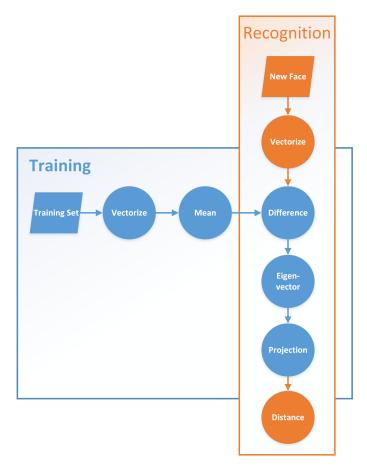

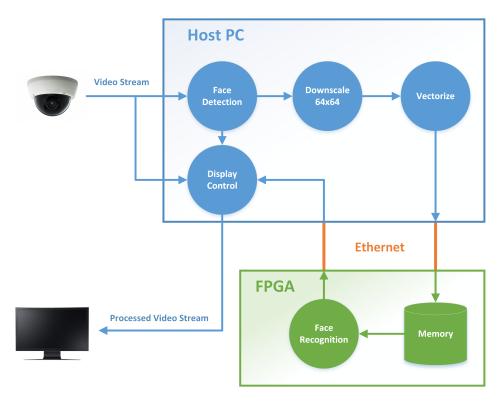

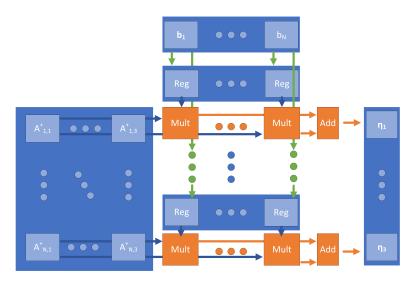

In the *Multi-channel Online Sorting* core a cluster mean consists of  $3 \times 3 \times 64$  data points, which are represented as 16 bit integers. The clusters are represented as fixed point type numbers, all of them are 18 bit with 2 bit fractional part. The single-channel OSort processes spikes with 64 samples using double precision. The memory required for cluster mean storage are less if integer values are used. The  $T_C$  classification threshold values are in the range of  $10^5$ , therefore rounding the values does not change the result of the comparison.

In this implementation for the calculation of the  $T_C$  classification threshold the  $c_C$  clustering correction factor was determined experimentally and set to 0.4 for all simulated data and 0.1 for the in vivo recording, while the number of sample points  $N_S$  were 64 for both cases.

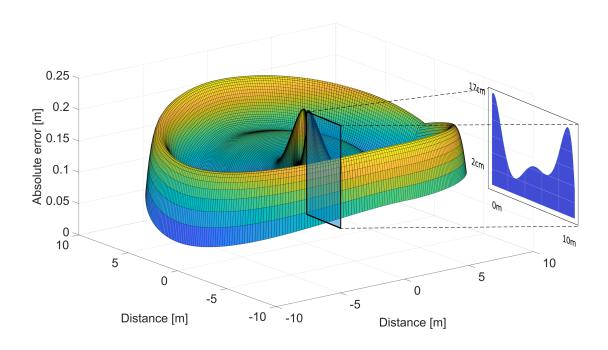

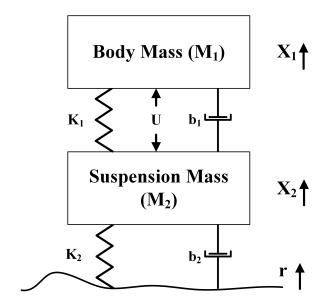

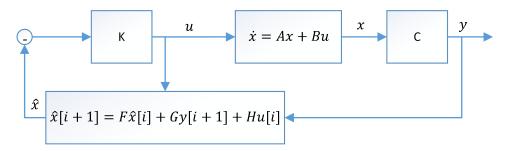

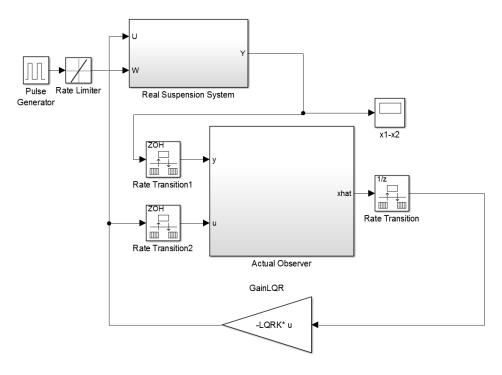

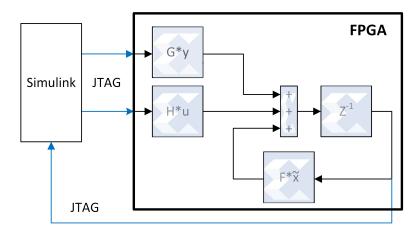

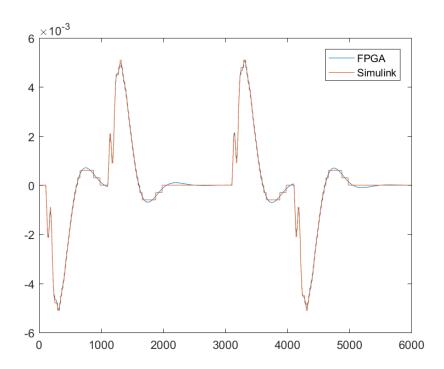

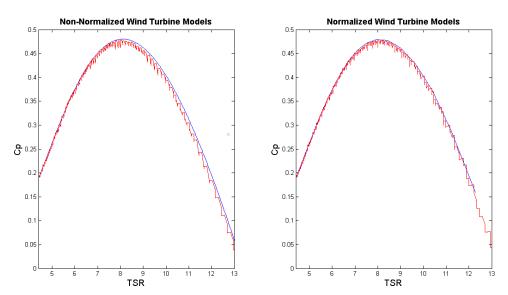

In this case a 18 bit wide and 2048 element deep configuration of Xilinx 7 series BRAMs are used, therefore, 32 clusters can be stored in 9 BRAMs. The number of clusters in the proposed system ( $32\times4$  electrode array) are expected to be around 100. Therefore the maximal number of clusters is 128 using 36 BRAMs. The computation of the *Multi-channel Online Sorting* core uses an array of processing elements with 9 ( $3\times3$ ) Arithmetic Units.